为什么要做8b/10b编码?

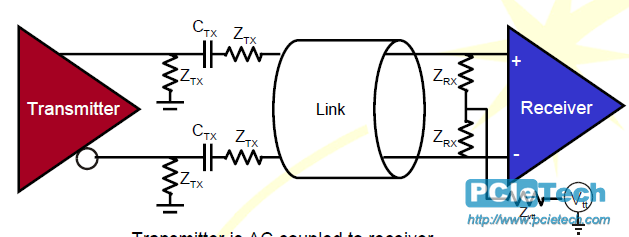

PCIe是采用差分信号传输的,而差分信号电气规范要求其发送端串接一个电容CTX,以进行AC耦合。该电容也被称为AC耦合电容。这个耦合电容用于隔直流、通交流(简单的理解,可以认为是仅让差分信号通过),并且在链路接收负载检测(receiver detect )也会用到,这个后续再讨论,这里不详细展开。

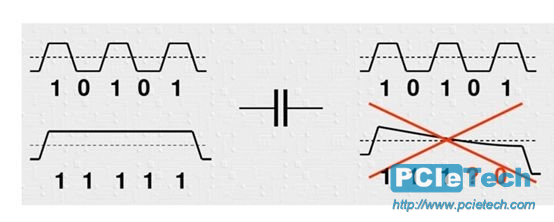

因为这个电容的存在,问题来了。当链路上连续出现多个0或者1的时候,“隔直”效应发生了,接收端的电压会下降,信号变得无法正确识别。故交流耦合信号传输中需要尽量做到直流平衡(DC Balance),直流平衡的意思是指在一组信号中0和1的个数相等,尽量避免连续多个1或者连续多个0,比如连续三个1/0之后,一定要插入一个0/1。

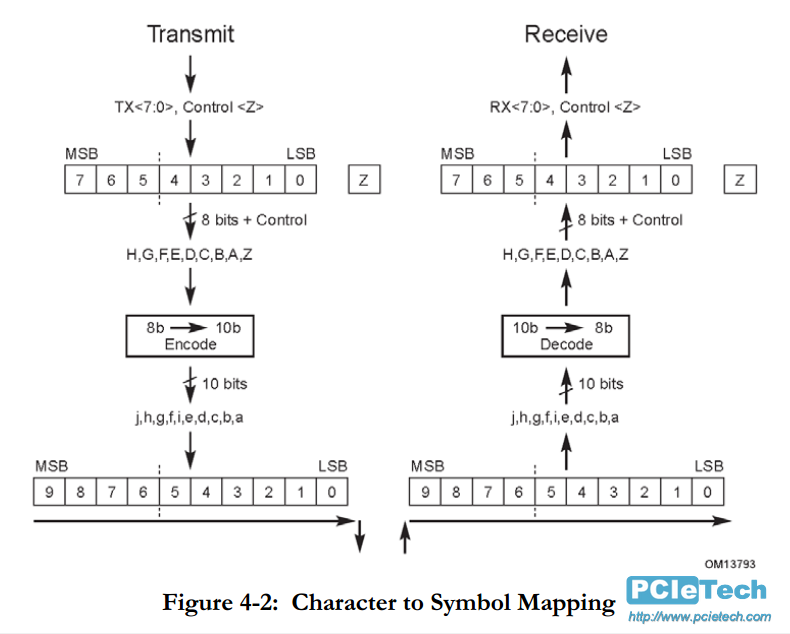

为了达成直流平衡,PCIe spec对数据进行了特别的编码,也就是8/10b编码和Gen3以后的128/130b编码。所谓的编码,直观理解就是把8b(128b)的数据编码成10b(130b)来传输,使得发送的“0”、“1”数量保持基本一致。接收端按照同样的编码规则,解析出8b(128b)原始数据即可。事实上很多其他高速信号传输也用到类似的编码方式。为什么编码后就可以保持“0”、“1”一致以及详细的编码方式可以参考协议。这里需要记住一个关键事实,因为有了编码,链路上传输的有效数据只占80%(8b/10b编码情况下。)

思考:

Gen2的8b/10b编码怎么和Gen3的128/130b编码对接?

![]() 数据在不同的lane上,是怎么分配传输的?

数据在不同的lane上,是怎么分配传输的?