Transmitter Elements of the Phsical Layer

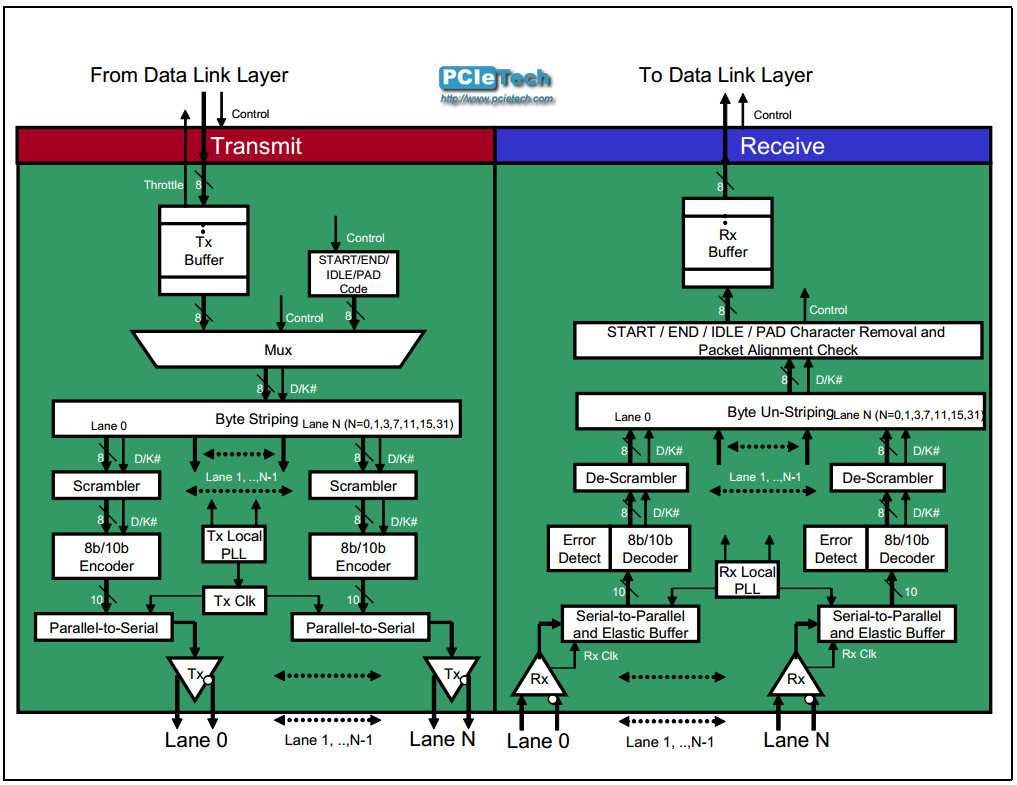

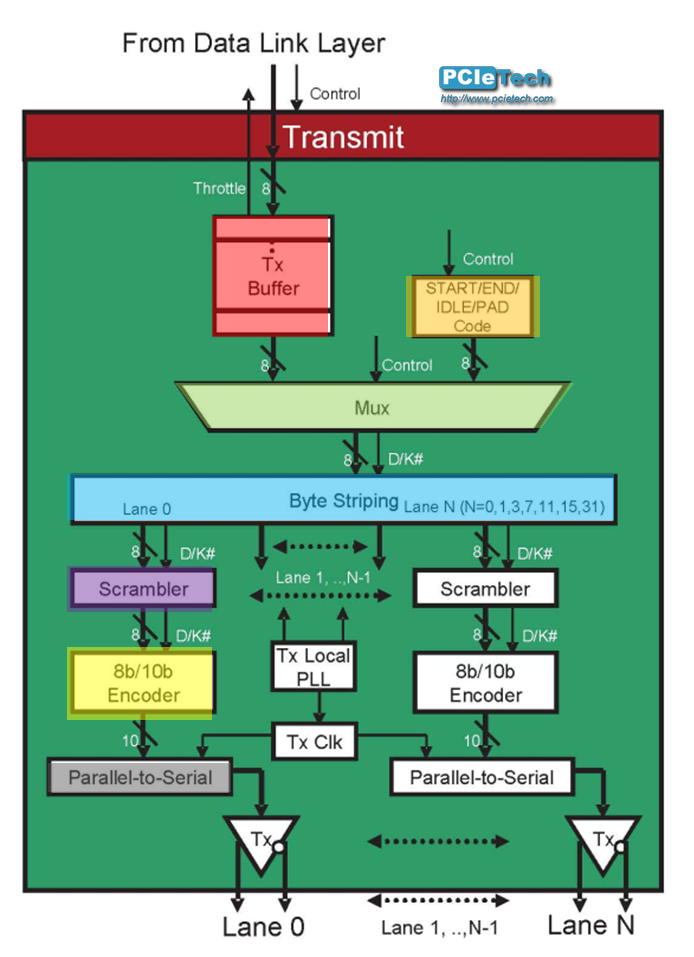

如上节所提到,物理层分为逻辑处理部分和电气部分。整个逻辑部分的处理框图如下:

简化一下,我们先来看看逻辑发送的部分:从数据链路层下来的数据报文TLP和链路层报文DLLP被放在发送缓冲区,被添加上控制字符(如start和end等),经过多路复用器分发到各条lane上。然后被扰频器加扰通过8b/10b编码或者128/130编码后,并转换发送到物理链路上。

发送缓冲区(Tx Buffer):没啥好说的,缓存数据链路层下来的数据。并在缓冲区溢出时,反馈给数据链路层流控。

控制字符(Control Code):区分发送的数据还是控制,生成不同的控制字符。

多路复用器(Mux):根据发送的内容不同选通不同的控制字符添加。

字节拆分(Byte Stripping):按照一定的规则,把数据流拆分成单个字节,并分发到不同的通道(lane)上,如2、4、8、16、32 lane。单lane的情况下不需要拆分。

扰频(Scrambler):也叫扰码,主要目的时防止高速链路上的EMI噪音。各位有兴趣可以参考相关的文档。注意:控制字符是不经过扰频的。

编码(8b/10b或者128b/130):按照一定的规则按字节编码。(前面文章已经讲过一些)

并转串(Parallel to Serial):没啥好讲的。:)

注:Gen3的发送逻辑增加了一些内容,但是整体上不影响对于发送逻辑的理解。